Zynq UltraScale+ MPSoCの内部メモリと外部メモリについて概要

BRAM・URAMと外部DDRメモリの違いなどが知りたい。(参考サイト)

Xilinx の FPGA 内部のメモリ階層は(中略)、分散 RAM (Distributed RAM), BRAM (Block RAM), URAM (Ultra RAM) の 3種は FPGA 内に実装されています。

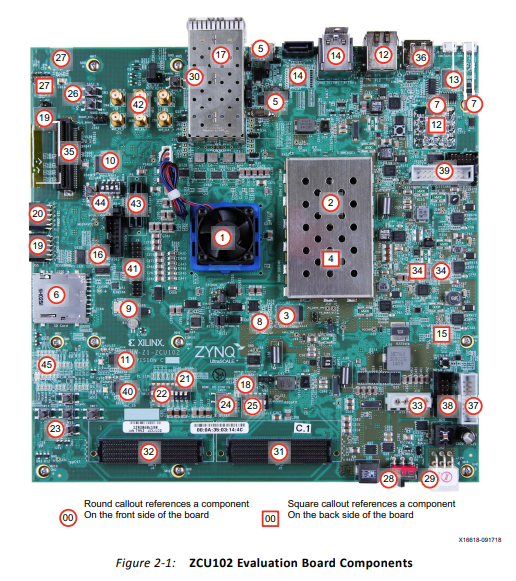

この”FPGA内”というのは次の写真の①のことかな。SoCのこと。

3つをざっくり説明すると...

【内部メモリ(RAM)】

・分散RAM:LUT を使用し、係数の格納、ステート マシン、および小規模バッファーとして有効。

・BRAM:高速かつ柔軟なデータ ストレージおよびバッファリングとして有効。

・URAM:各ブロック 288Kb のストレージを提供し、またブロックを接続して大規模なオンチップ ストレージを構築できます。(引用元)

内部メモリと比較して、外部メモリは次のようになっている(Zynq UltraScale+ MPSoCの場合)。

【外部メモリインタフェース】

Zynq® UltraScale+™ MPSoC には、プロセッシング システム内にハード メモリ コントローラーが含まれています。これらのデバイスは、32GB のアドレス可能なメモリをサポートできます。その他のメモリは、プログラマブル ロジック領域に追加できます。

上の表にある全てが搭載されるんじゃなくて、デバイスごとに搭載されるメモリは違うよね。

次に示すFigure3-1はMPSoCのブロックダイアグラムだけど、赤い円で囲った部分が「プログラマブルロジック メモリソリューション」のことかな。

(PSメモリソリューションはFigure2-1の②)

Programmable Logic の中にはBRAMやURAMなどの「内部メモリ」がある、という認識でいいだろうか。

もっと詳しいことは...ZCU102の場合UG1182に書いてあるからいつか見よう。今日は概要だけつかみたい。

次に、研究している自己組織化マップのハードウェアについてVitisでSystem DIagramを見てみる。

URAMはN/Aとなっているが、ビルド対象としたZCU102はURAMが使えない?

調べてみたら、使えるみたい。じゃあ単に利用してないのか。

↓小さいので抜き出してみた

UltraRAMは36Mb使えるみたい。

BRAMは最大で36Mbとなっていて、1つ36Kbだから865個で31140Kb。大体94.85%に近い値かな。

自分の書いたソースコードのうち、どの記述がBRAMを消費しているのか把握しよう。多分、カーネルで定義した配列はBRAM領域(=内部メモリ)を使うっぽい?

次に知りたいこと・疑問

・難しそうだけど、FPGAの内部メモリ(カーネル)とグローバルメモリ(ホストとカーネル共用のメモリ)のアクセス方法について知りたい。

・enqueueMigrateMemObjectsのおさらい