UG573を読んでXilinx UltraScaleのBRAMの概要を知りたい

UltaraScale アーキテクチャ メモリリソースユーザーガイド(UG573)

を読んで、いまだによく分かっていないBRAMを学ぶ。

(間違ってること書いてたらスミマセン。)

ブロックRAMの概要

UltraScale アーキテクチャデバイスのブロックRAMは2つの独立した18Kb RAM または 1 つの 36Kb RAM として構成可能で、いずれも最大 36キロビットのデータを格納できます。

1個のBRAMが36Kbのメモリと考えてよいのかな。

図1-1はBRAMをTDP(True Dual Port)モードで使用した場合の図で、18Kbの領域が2つあると考えるらしい。

それぞれの領域にアクセスできるポートがあって、読み出し・書き込みについて完全に独立している。クロックも別のものを利用できる。

各ブロックRAMには書き込みポートと読み出しポートが 2つずつあります。36KbブロックRAMをTDP (True Dual Port) メモリとして使用する場合、ポートの幅は個別に 32Kx1、 16Kx2、 8Kx4、 4Kx9、 2Kx18、 1Kx36 のいずれかに設定でき ます。

これって、例えば8Kx4っていうのは4ビットx8Kのポート幅という意味なんだろうか?

36KbブロックRAMをSDP(SimpleDualPort)メモリとして使用し、書き込みポートと読み出しポートをそれぞれ1つずつしか使用しない場合は、512x72ビットのポート幅も可能です。

なるほど。

72ビットって、1度に読み出せるのかな?そうすると、データバス幅が72ということ?それは可能なのか?よく分からない。

隣接するブロックRAMをカスケード接続し、下段のブロックRAMのデータ出力を上段のブロックRAMに入力することで、大容量のブロックRAMブロックを構成可能です。

これで32Kb以上のメモリ領域を使えるということかな。

BRAMの数はFPGAデバイスごとに異なるから、全体で使えるBRAMの記憶領域も違ってくる。

あと、FIFOとして使うことができるらしい。

ブロックRAMの説明

ブロックRAMは、デバイス全体でクロック領域(CR)内にカラム状に配置されます。

このCRというのは、PL領域にあるという認識でいいのかな?

ちなみにちょっと脱線するけどUG1182を眺めてたらXCZU9EG MPSoCのブロックダイアグラムがあったから載せておく。

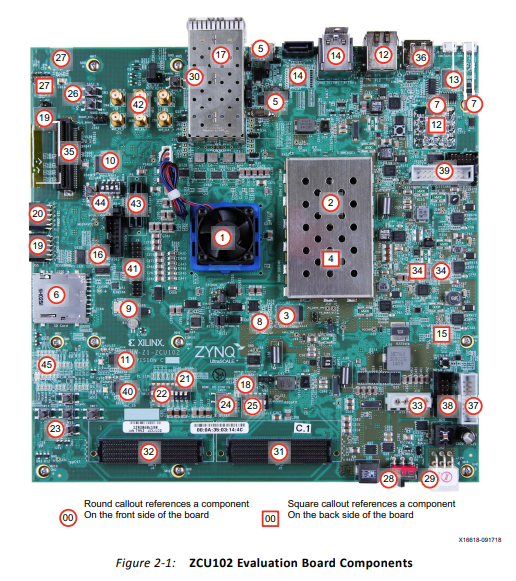

下に載せたFigure 2-1の①が上のBlock Diagram。

今更だけどSoCの中身とか全然分かってなかった。上はZCU102の例。Figure3-1にCortex-A53ってのが4つあって、すなわちこれがクアッドコアARM。

これから少しずつ詳しくなっていきたいな。

あと下の図がXilinxのMPSoC。これがFigure2-1の①だ。こうやって比較して見ると分かりやすい。

![]()

話をBRAMに戻そう。

なんだか分かったようでまだ全然分かってない。

そもそもどこにあるのか?どんなときに使うのか?よく分からなくなってきた。一旦、先生に聞いてみよう...。

最後にブロックRAMとUltraRAMの比較表を載せておく。UltraRAMっていうのは、まだよく分かってないけどBRAMに似たものらしい。違いは表2-1にある。

まだまだ分からないことが膨大にあるけど少しずつ詳しくなっていきたいなあ。

今日はこの辺でやめとこう。

次に知りたいこと・疑問

・BRAMってPL部にある、という認識でよいのか?

・UltraRAMについて

・BRAMとUltraRAMを使うには?グローバルメモリとは?